#### k=m=880

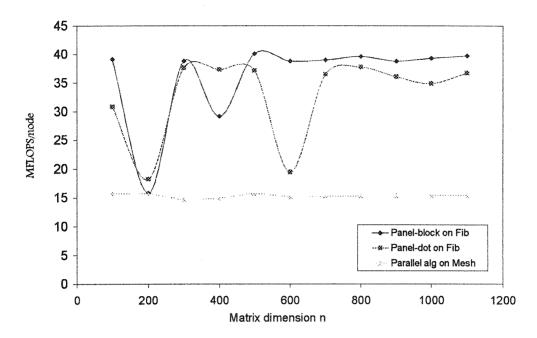

Figure 7: Performance of various parallel matrix multiplication algorithms

#### 6. References

- S. G. Akl, The design and Analysis of Parallel Algorithms, Queens University, Prentice Hall International, Inc, 1989.

- A. V. Anisimov, "Fibonacci Hypercube", International Journal of computer mathematics, Vol. 25,pp. 221\_227, 1997.

- A. Chtchekanova, J. Gunnels, G. Morrow, J. Overfelt, R. geijn, "Parallel Implementation of BLAS: General Techniques for level3 Blas", TR\_95\_40, Department of Computer Sciences, University of Texas, Intel Research council, 1995.

- [4] G. C. Fox, M. A. Johnson, G.A. Lyzenga, S. Wotto, J. K.Salmon and D. W. Walker, Solving Problems on Concurrent Processors, Prentice Hall, Englewood cliffs, N. J. Vol.1, 1998.

- [5] J. Gunnels, C. Lin, Greg Morrrow, R. Geijn, "Analysis of a Class of parallel Matrix Multiplication Algorithms", A Technical Paper Submitted to IPPS 98, 1998.

- [6] R. Geijn, "Scalable Universal Matrix Multiplication Algorithms , Concurrency": Practice and Experience, Vol. 9(4), pp. 255\_274 ,1995.

- [7] R. V. Geijn,"Using PLAPACK: Parallel Linear Algebra Package", The MIT Press, 1997.

- [8] B. Grayson, A. Pankaj shah, R. Geijn, "A High Performance Strassen Implementation", Intel Research council, June 13. 1995.

- J. M. Jadish, Parallel Algorithms and Matrix Computation, University of Cambridge, Clarn Don Pess. Oxford, 1998.

- [10] L. Jokar, "Parallel Algorithms for Matrix Multiplication", M.S Thesis, Department of mathematics and computer science, Tehran university, 2002.

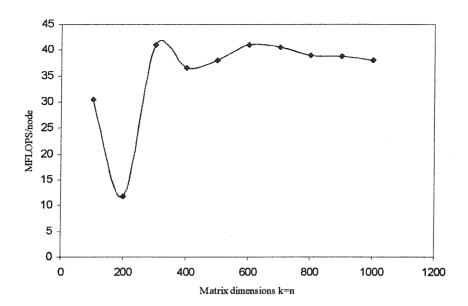

Figure 5: Performance of parallel matrix multiplication algorithm based on panel-block that designed to run on  $C_{F,4}$

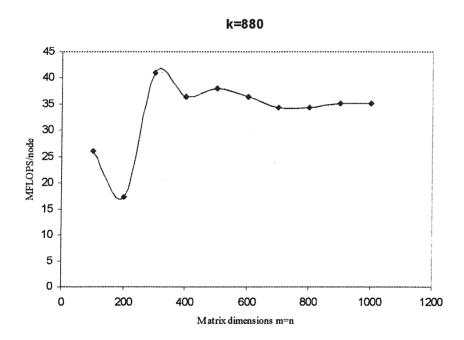

Figure 6: Performance of parallel matrix multiplication algorithm based on panel-dot that designed to run on  $C_{F,4}$ .

matrix multiplication algorithm based on panel-block that are designed to run on  $C_{F,4}$ . For the case where  $m>>n_1f_{n_1+2}$ , this algorithm is cost-optimal, we present results for the case where m dimension is fixed and large. It is clear from the graph (in accordance to the Figure 5) that to increase dimension of k in comparison to the dimension of m, the speed of performance of algorithm will be reduced. Therefore if dimension of m is fixed and large this algorithm will be an improved algorithm.

In Figure 6, we show the performance of parallel matrix multiplication algorithm based on panel-dot that are designed to run on  $C_{F,4}$ . Considering, for the case where  $k >> n_1 f_{n_1+2}$ , this algorithm is cost-optimal, we present results for the case where k dimension is fixed and large. It is clear from the graph (in accordance to the Figure 6) that to increase dimension of m in comparison to the dimension of k, the time of algorithm performance will be increased. Therefore if dimension of k is fixed and large this algorithm will be an improved algorithm.

In Figure 7, the results of the performance of panelblock and panel-dot algorithms that are designed to run on  $C_{F,4}$  and parallel multiplication algorithm that is designed to run on a 4×2 mesh structure [1] were compared. We present results for the case where both dimensions of k and m are fixed and large. It is clear from the graphs that the panel-block algorithm has a better performance time in respect to the other two algorithms. Also, the performance time of both panel-block and panel-dot algorithms on the Fibonacci hypercube structure were much better than performance time of the parallel multiplication algorithm on the mesh structure.

#### 5. CONCLUSION

The main drawback of the hypercube structure, is the necessary increase of each vertex valence while increasing a hypercube dimension. This means that the value of the communication hardware grows faster than a hypercube dimension. Taking into consideration that increase of the hypercube dimension and vertices of higher dimensional mesh will lead to a considerable rise in the number of connections of processors and consequently this will lead to a fast growth in the hardware. By using the presented algorithms on the Fibonacci hypercube structure, the cost of connection amongst the processors will be reduced (because the Fibonacci hypercube structure has the same property as hypercube structure but with fewer connectors plus the same number of vertices).

The panel-block algorithm is designed to run on  $C_{F,n_1}$  structure. As we know the number of processors in this structure is  $f_{n_1+2}$ , where  $n_1$  is Fibonacci hypercube dimension. As shown in the previous sections,

algorithm time of this is complexity  $Q(knn_1t_w + \frac{knm}{f_{n_1+2}})$  and the case where

$m>>n_1f_{n_1+2}$  , this algorithm is cost-optimal. In accordance to the procedure of this algorithm, the steps of algorithm will be repeated by n\*k/2 times, therefore, if

the dimension of m is fixed and large, this algorithm would have a better performance time in comparison to the panel-dot algorithm.

The panel-dot algorithm on the Fibonacci hypercube structure with dimension of  $n_1$  uses  $f_{n_1+2}$  processors. As shown in the previous sections, the time complexity of this algorithm is  $O(nmn_1t_w + \frac{knm}{f_{n_1+2}})$  and for the case

where  $k \gg n_1 f_{n_1+2}$ , this algorithm is cost-optimal. Since the steps of this algorithm will be repeated by n\*m/2 times, therefore, if the dimension of k is fixed

and large, this algorithm in comparison with panel-block algorithm has a better performance time.

Comparing the graph of the charts in the Figures 5 and 6 it can be said in the points where k > m, the speed of performance of panel-dot algorithm is higher than panelblock algorithm. And in the points where m > k, the panel-block algorithm has a better performance time than pane-dot algorithm.

Considering dimension of m has a fixed large quantity, the panel-block algorithm in comparison with the paneldot algorithm will take less time to process and if considering dimension of k has a fixed and large quantity, the panel-dot algorithm in comparison to the panel-block algorithm will take less time to process.

As it is seen in the Figure 7, when both dimensions of k and m are fixed and large, the panel-block algorithm has a better performance time than panel-dot algorithm and parallel multiplication algorithm on mesh structure. Also, the performance time of both panel-block and panel-dot algorithms on the Fibonacci hypercube structure are much better than the performance time of the parallel multiplication algorithm on the mesh structure.

$$Cost = T_P * P = O(knn_1 f_{n_1 + 2} + knm). \tag{10}$$

We know the condition of cost-optimality is:

$$E = \frac{T_{Seq}}{P * T_P} = O(1). \tag{11}$$

Therefore to have cost -optimal algorithm we must

$$knn_1 f_{n_1+2} << knm$$

$$\Rightarrow n_1 f_{n_1+2} << m.$$

(12)

Therefore, for the case where  $n_1 f_{n+2} \ll m$  the algorithm is cost-optimal.

B. Parallel Matrix Multiplication Algorithm Based on Panel-dot

Consider  $C_{F,n_1}$  structure, as we know the number of processors in this structure is  $f_{n_1+2}$ , where  $n_1$  is Fibonacci hypercube dimension. Assume A and B are two matrices with  $m \times k$  and  $k \times n$  dimension. Matrix A will be divided to row panel with b size, and Matrix Bwill be divided into column panel with  $b \times b$  dimensions. Therefore, we would have:

$$\begin{bmatrix} C_{0,0} & \cdots & C_{0,n/b} \\ \vdots & \vdots & \vdots \\ C_{m/M}, 0 & \cdots & B_{m/b}, n/b \end{bmatrix} = \begin{bmatrix} \hat{A}_0 \\ \hat{A}_1 \\ \vdots \\ \hat{A}_{m/b} \end{bmatrix} (B_0 \mid B_1 \mid \dots \mid B_{n/b})$$

$$= \begin{bmatrix} \hat{A}_0 B_0 & \cdots & \hat{A}_0 B_{n/b} \\ \vdots & \vdots & \vdots \\ \hat{A}_{m/b} B_0 & \cdots & \hat{A}_{m/b} B_{n/b} \end{bmatrix}$$

(12)

This algorithm is designed based on multiplication of row panels of A by column panels of B. This multiplication is called multiplication of panel-dot. In this algorithm, from multiplication of row panel  $\hat{A}_{S}$  by column panel  $B_h$ , block  $C_{s,h}$  of matrix C will be obtained.

In this algorithm, the following steps will be repeated by  $n_h \times m_h$  times.

- 1) Members of panel  $\hat{A}_S$  will be distributed amongst all processors in the vector based method

- 2) Members of panel  $B_h$  will be distributed amongst all processors in the vector based method.

- 3) The result of C(i)=A(i)\*B(i) will be computed by all the processors simultaneously.

- 4) With sum to one processor, the result will be saved in  $C_{s,h}$ .

Algorithm procedure is shown as follows: Procedure Fib\_Panel\_dot\_Multip(A, B, C)

Begin

For

$$h=0$$

to  $m/b$  Do

For  $s=0$  to  $n/b$  Do

Begin

For  $i=0$  to  $f_{n_1+2}$  Do in Parallel

Begin

$A(i) \leftarrow A_{h,i}$ ;

$B(i) \leftarrow B_{i,S}$ ;

$C(i) = A(i) \times B(i)$ ;

end

Sum\_to\_one( $C_{h,S}$ );

end

end.

Figure 4: Panel \_dot Algorithm in  $C_{F,n_1}$  structure

## Cost-Optimality:

The first and second steps of algorithm take constant time. In the third step, the multiplication of two matrices with the dimensions of  $b \times \frac{k}{f_{n_1+2}}$  and  $\frac{k}{f_{n_1+2}} \times b$ will be computed by all the processors simultaneously. Therefore, this multiplication takes  $(b^2 * \frac{k}{f_{n_1+2}})$  time.

The fourth step of algorithm takes  $(t_s + b^2 t_w)n_1$  time. There are  $\frac{n}{b} \times \frac{m}{b}$  iterations of steps 1 to 4 [10]. Thus, the algorithm time complexity is equal to:

$$\begin{split} T_P &= O(\frac{n_b' * m_b'}{b} (b^2 * \frac{k}{f_{n_1 + 2}} + (t_s + b^2 t_w) n_1)) \\ &= O(\frac{knm}{f_{n_1 + 2}} + nmn_1 t_w). \end{split}$$

Then cost of algorithm will be equal to:

$$Cost = T_P * P = O(knm + nmn_1 f_{n_1 + 2}). \tag{15}$$

We know the condition of cost -optimality is:

$$E = \frac{TSeq}{P*TP} = O(1). \tag{16}$$

Therefore, to have cost -optimal algorithm we must have

$$\begin{aligned} & \operatorname{nmn}_1 f_{n_1 + 2} << k \operatorname{nm} \\ & \Rightarrow n_1 f_{n_1 + 2} << k. \end{aligned}$$

Therefore, for the case where  $n_1 f_{n_1+2} \ll k$  the algorithm is cost-optimal.

#### 4. Performance results

This section reports the performance of the algorithms that we presented in the previous sections, on a system with 8 nodes.

In Figure 5, we show the performance of parallel

(14)

```

If P_0 did not receive the data then P_0 \leftarrow x;

If n=0 Return();

If n=1 then P_0 Send Data to P_1;

Else

/*adjacent function returns the

adjacent

processor P<sub>0</sub> that is in bit nth differ.*/

P_0 Send Data to adjacent(P_0,n);

do in parallel

Broadcast Fib(n-1,x);

Broadcast_Fib(n-2,x);

}

```

Figure 2: Broadcasting algorithm in Fibonacci hypercube  $C_{F,n}$

# E. Model of Communication Cost

We will assume that in the absence of network conflict. sending a message of length n between any two nodes can be models by:

$$t_s + nt_w. (7)$$

where  $t_{\star}$  represents the latency (startup cost) and  $t_{w}$ represents the cost per byte transferred.

#### 3. PARALLEL ALGORITHMS

In this part, two optimal parallel algorithms are given for the matrix multiplication on the Fibonacci hypercube structure. We show these algorithms are cost-optimal.

Parallel Matrix Multiplication Algorithm Based on Panel-block

If we consider  ${}^{C}F, n_1$  structure, as we know the number of processors in this structure is  $f_{n_1+2}$  that  $^{n_1}$  is Fibonacci hypercube dimension. Assuming A and B are two matrices with  $m \times k$  and  $k \times n$  dimension, Matrix A will be divided into column panel each with b size, and Matrix B will be divided into blocks with  $b \times b$ dimensions. Therefore, we would have:

$$(C_{0}|C_{1}|...|C_{n/b}) = (A_{0}|A_{1}|...|A_{k/b})\begin{bmatrix} B_{0,0} & ... & B_{0,n/b} \\ \vdots & \vdots & \vdots \\ B_{k/b}, 0 & ... & B_{k/b}, n/b \end{bmatrix}$$

$$= (A_{0}B_{0,0} + ... + A_{k/b}B_{k/b}, 0 | ... | A_{0}B_{0,n/b} + ... + A_{k/b}B_{k/b}, n/b ).$$

$$(8)$$

This algorithm is designed based on multiplication of column panels of A by blocks of B. This multiplication is called multiplication of panel-block. In this algorithm, from the sum of multiplication of the column panels of matrix A by block of i<sup>th</sup> column of matrix B, panel  $C_i$ of matrix C will be obtained.

In this algorithm the following steps will be repeated by

$$n/h \times k/h$$

times.

- 1) Members of panel  $A_{S}$  will be distributed amongst all the processors in the vector based method.

- 2) A block from matrix B, will be distributed in every processor.

- 3) The result of C(i)=C(i)+A(i)\*B(i) will be computed by all the processors simultaneously.

- 4) After the steps 1 to 3 repeated by  $\frac{k}{b}$  times. In gathering operation, a panel of matrix C will be computed.

Algorithm procedure is shown as follows: Procedure Fib Panel block Multip(A, B, C)

egin

For

$$h = 0$$

to  $n/b$  Do

Begin

For  $i = 0$  to  $f_{n_1+2}$  Do in Parallel

$C(i) \leftarrow 0$ ;

For  $s = 0$  to  $k/b$  Do

Begin

For  $i = 0$  to  $f_{n_1+2}$  Do in Parallel

$A(i) \leftarrow A_{i,S}$ ;

Broadcast\_Fib $(n_1, B_{S,h})$

For  $i = 0$  to  $f_{n_1+2}$  Do in Parallel

$C(i) = C(i) + A(i) \times B(i)$ ;

end

Gather to  $C_h$ ;

end

end.

Figure 3: Panel-block Algorithm in  $C_{F,n_1}$  structure

# **Cost-Optimality:**

In the first step of algorithm,  $A_s$  in the constant time will be distributed amongst all the processors in the vector based method. The second step of algorithm takes  $(t_S + b^2 t_W)n_1$  time. In the third step, the multiplication of two matrices with the dimensions of  $\frac{m}{f_n} + 2^{\times b}$  and  $b \times b$  will be computed by all the processors simultaneously. Therefore, this multiplication takes  $(\frac{m}{f_{n_1+2}}*b^2)$  time. The fourth step takes constant

time. There are  $\frac{n}{b} \times \frac{k}{b}$  iterations of steps 1 to 4 [10]. Thus, the algorithm time complexity is equal to:

$$T_{P} = O(\frac{k}{b} * \frac{n}{b} ((t_{s} + b^{2}t_{w})n_{1} + \frac{m}{f_{n_{1}+2}} * b^{2}))$$

$$= O(knn_{1}t_{w} + \frac{knm}{f_{n_{1}+2}}).$$

(9)

Then cost of algorithm will be equal to:

dimension. We assume that the  $C_{F,n}$  shows a Fibonacci hypercube with a number of  $f_{n+2}$  vertices which in that index, each vertex can be shown with n bit. Fibonacci

hypercube with n dimension can be presented as n Fibonacci hypercube.

If we show the connections of the processors as a graph, therein the set of all edges in  $C_{F,n}$

presented as  $E_n$  and the set of all labels of vertices of  $C_{F,n}$  structure presented as  $FC_n$  . Also the number of vertices of  $C_{F,n}$  can be presented by  $|FC_n|$ .

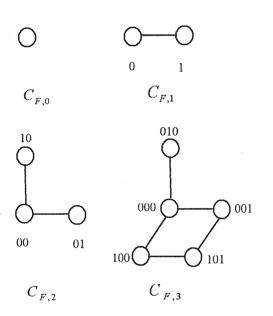

In Figure 1, Fibonacci hypercubes  $C_{F,0}$  ,  $C_{F,1}$  ,  $C_{F,2}$ ,  $C_{F,3}$  are depicted.

Figure 1: Fibonacci hypercubes  $C_{F,0}$ ,  $C_{F,1}$ ,  $C_{F,2}$ ,  $C_{F,3}$

B. Properties of the Fibonacci Hypercube 1<sup>st</sup> Property:  $FC_{n+1}=0FC_n+10FC_{n-1}$ . (1) 2<sup>nd</sup> Property:

$$FC_{n+k} = FC_k \, 0FC_{n-1} + FC_{k-1} \, 010FC_{n-2} \tag{2}$$

$3^{\rm rd}$  Property: Number of vertices of  $C_{F,n}$

4th Property: If a and b are adjacent vertices in  $C_{F,n}$ then H(a,b)=1 [2] and if  $a,b \in FC_n$  and H(a,b)=1then a and b are the adjacent vertices in  $C_{\pi n}$ .

## C. Data Decomposition

For simplicity, we will assume that the dimensions m, n and k are integer multiples of the algorithmic block size b. When discussing these algorithms, we use the following partitioning A, B and C:

$$X = (X_{\circ}|X_{1}| \cdot \cdot |X_{n_{X}}|) = \begin{pmatrix} \frac{\hat{X}_{0}}{\hat{X}_{1}} \\ \vdots \\ \hat{X}_{n_{X}}| \end{pmatrix}. \tag{3}$$

where  $X \in \{A, B, C\}$  and  $m_x$  and  $n_x$  are the row and column dimension of the indicated matrix.

$$X = \begin{pmatrix} X_{0,0} & X_{0,1} & \cdots & X_{0,n_{X/b}} \\ X_{1,0} & X_{1,1} & \cdots & X_{1,n/b} \\ \vdots & \vdots & \vdots & \vdots \\ X_{m/b}, 0 & X_{m/b}, 1 & \cdots & X_{m_{X/b}, n_{X/b}} \end{pmatrix}. \tag{4}$$

In the above partitioning, the block size b is chosen to maximize the performance of the local matrix-matrix multiplication operation.

## D. Data Distribution

#### I): Vector based matrix distribution

It is more natural to start by distributing the problem to nodes, we partition vector x and assign portions of this vector to nodes. The matrix A is then distributed to nodes so that it is consistent with the distribution of the vectors, as we describe below.

Assume that we have p processors. We use the following partitioning

$$x = \begin{pmatrix} x_0 \\ x_1 \\ \vdots \\ x_{p-1} \end{pmatrix}. \tag{5}$$

This vector is distributed by assigning  $x_i$  to  $P_i$ . We call such matrix distribution, vector based.

II): Broadcasting a datum to Fibonacci hypercube architecture

We broadcast a datum to Fibonacci hypercube  $C_{F,n}$ with O(n) time complexity. According to the first property and structure of Fibonacci hypercube the following identities for time complexity can be obtained:

$$T(C_{F,n}) = T(C_{F,n-1}) + 1 = T(C_{F,n-2}) + 2 = \dots = T(C_{F,0}) + n$$

$$T(C_{F,n}) = T(C_{F,0}) + n$$

$$T(C_{F,0}) = 1$$

$$\Rightarrow T(C_{F,n}) = O(n).$$

(6)

The algorithm for broadcast to  $C_{F,n}$  is as follows:  $Broadcast_Fib(n,x)$

12

# Optimal Parallel Matrix Multiplication Algorithms On a Fibonacci Hypercube Structure

L. Jokar<sup>i</sup>; H. Ahrabian ii

#### ABSTRACT

In this paper, we give two new optimal parallel algorithms for matrix multiplication which are designed to run on a Fibonacci hypercube structure. At first, we present a broadcast algorithm on Fibonacci hypercube with O(n) time complexity. We use this broadcast algorithm and algorithms presented by Gunnels. Lin, Morrow and Geijn on a mesh structure, in order to present two optimal parallel matrix multiplication algorithms on a Fibonacci hypercube structure. We show these algorithms are cost-optimal. The performance of the algorithm has been tested on a simulative parallel system.

#### KEYWORDS

Broadcast, Cost-Optimal, Fibonacci Hypercube, Matrix Multiplication.

#### 1. Introduction

In the last three decades, numerous parallel algorithms were implemented for the matrix multiplication. The most common parallel matrix multiplication algorithms were Fox's algorithm, Cannon's algorithm, Strassen's algorithm and parallel algorithms which were designed to run on Mesh and Hypercube structures [1], [4], [8], [9]. In 1998, Gunnels, Lin, Morrow and Geijn with regard to various dimension sizes of matrixes, presented 5 parallel algorithms for the multiplication of matrixes on a mesh structure [3], [5], [6], [7].

As you know, all the parallel computers consist of many types of Mesh, Hypercube and Perfect shuffle structures. Even though the Hypercube structures are very useful, they also have their own problems. More of Hypercube dimensions will lead to a rise in the number of processors and connection between them. Consequently, this will lead to a fast growth in the hardware. For this reason, in recent years researchers were searching for a new structure which could substitute the hypercube and to eliminate this problem to some extent. In 1997, the Fibonacci hypercube structure was recommended by Anisimov [2]. Anisimov proved that the Fibonacci hypercube has the same property as hypercube but with

fewer connectors plus the same number of vertices.

In this paper, we give two new optimal parallel algorithms for matrix multiplication which are designed to run on this structure. We show these algorithms are costoptimal.

#### 2. BACKGROUND

# A. The Fibonacci Hypercube Structure

The Fibonacci hypercube was introduced by Anisimov [2] initially in 1997. This Fibonacci hypercube is a new topological structure that is obtained recursively using formulas similar to the relation of Fibonacci numbers. It has properties very close to the hypercube. In this part, a very brief explanation is given:

Assume that we processors

$$p_0, p_1, ..., p_{P-1}$$

Knowing that p is a Fibonacci number and for each processor a binary index is attributed which the binary representation of numbers is substituted by the representation of numbers by sums of Fibonacci numbers. Each processor will be connected to the vertices that their index differs by just in one position. They called this structure the Fibonacci hypercube. In this structure, the number of bits which form the index of vertices is called

i. L. Jokar was M.S Student, Department of Computer Science, School of Mathematics, Statistics, and Computer Science, University of Tehran, Tehran, Iran and is an Educator, Department of ComputerEngineering, Islamic Azad University, University of Rodehen, Tehran, Iran.

ii. H. Ahrabian is an Assistant Professor, Department of Computer Science, School of Mathematics, Statistics, and Computer Science, University of Tehran, Tehran, Iran.